由新浪财经客户端、新浪科技联合主办的“2022科技风云榜”线上年度盛典今日开幕。英特尔研究院副总裁、英特尔中国研究院院长 宋继强在《新算力时代,实现万亿晶体管》主题演讲中指出,英特尔有信心在2030年实现在单个设备上达到1万亿的晶体管的目标。

持续长期的算力,是支撑各行业数字化转型升级的重要力量。通过长期的市场调研及客户沟通,英特尔发现,全球数据量正呈指数级增长,预计2020年往后十年数据量将呈指数级上升,未来会达到10的30次方。此外,数据的形态也正呈现出多样化趋势,现在大部分的数据还是通过人工、程序化等方式去定义并处理数据,而在未来,非常多的数据是通过传感器的感知进入到数字世界,必须要通过AI等技术去进行处理,并实时反馈到物理世界中去。

英特尔发现,未来的数据量和质的变化一定需要新的算力去支持,而不是现在的方法就可以完全支撑的。因此,英特尔对未来算力的支持有很高的预期,并且推测到2030年,单一个设备中将具备1万亿个晶体管。

“现在一个设备中有1千亿个晶体管,到2030年有1万亿个晶体管,在未来7-8年是10倍的增长,这样的增长速率仍然是符合摩尔定律的。而且通过英特尔很多部门的产品性能分析可以看到,基本上也是维持这样的一个增长速率。”宋继强表示。

推动摩尔定律不断前进,持续提高芯片集成密度

宋继强看到,在未来几年间,通过采用RibbonFET环绕栅极晶体管技术、PowerVia背部供电技术等制程工艺,同时引入High-NA EUV光刻机并且叠加2.5D、3D封装技术,都将有助于实现更高的设备晶体管集成度。

随着半导体制程工艺逐渐接近1纳米,甚至说推进到埃米级,继续靠晶体管萎缩来达到更高的集成度会越来越困难,成本也越来越高。为了进一步达到在单设备里增加晶体管密度的目的,通过先进封装技术让多个制成工艺节点的芯片集成在一起,让更大的裸片复合成为可能。

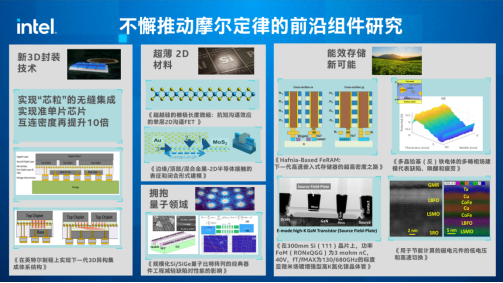

据宋继强介绍,在最近的IEDM国际学术大会上面,英特尔发布了8个关于前沿组件技术方面的研究,这些技术能够帮助英特尔持续推动摩尔定律不断前进。

其中,英特尔发布的3D封装技术,通过Hybrid Bonding实现芯力的无缝集成,把现在的单芯片级别芯片互连之间的间距从10微米继续缩小到3微米级别,是的互联密度提升了10倍。

此外,通过使用新的超薄2D材料,英特尔还可以在未来的晶体管中去替代硅作为通道材料,进一步抵抗短沟道效应,提高晶体管的效率和降低功耗。通过布局新的存储器件技术研究,能够去达到更高的存储密度,降低存储时延,从而使未来在嵌入式存储器里面达到更高的密度……

持续超能异构,搭建软硬一体的芯片生态

有了这些新的技术制造出来的半导体材料,英特尔就有了更多的在架构上去创新的机会。

根据处理数据的类型,目前英特尔推出的“芯片”其实可以分为CPU、GPU、IPU、IPGA或者AI专用加速器等,然而,开发者在基于不同芯片开发的时候通常会面临着不同的技术问题,而且很难在多架构上进行编程。因此,如何让未来的软件开发人员可以非常容易地使用到这些不同架构芯片的能力,让他们的程序在未来的新的XPU产生的情况下继续保持兼容性?成为了英特尔需要努力的方向。

据宋继强介绍,通过开展异构计算布局,英特尔打造了一个集XPU硬件、oneAPI软件以及UCle开放标准于一体的软硬一体化生态平台。

其中,oneAPI是一个建立在开放统一的跨架构社区编程的模型,在这个社区上,英特尔通过推动一种基于标准的统一软件堆栈,去统一描述底层的、源自于不同硬件厂商的CPU、GPU、XPU等硬件能力,然后再通过各种不同的高性能库去封装这些底层硬件的能力,并且允许通过业界标准的clk编程语言直接对这些硬件能力进行编程,让上层的应用和服务更加关注于软件或者运用的实现,不需要过多的关心底层的硬件技术原理及演进。

此外,英特尔还积极地推动建立了UCle这样的一个开放联盟,首先把英特尔相关的处理器、D2D I/O技术,以及一些多芯片互连通信的技术、协议等都推送在这个标准里。同时也会去支持对接诸如Arm Risc等其他不同种类的芯片,保证让各个厂商生产出来的硬件,都可以首先在物理层它们的电器层面进行无缝对接,进一步实现信号数据传输协议层的统一。

“总之,在未来的芯片半导体这个领域需要非常多的各种各样的技术,在开放的领域去探讨和共进,我们相信在这个领域,创新是永不止步的,我们非常有信心在2030年实现在单个设备上达到1万亿的晶体管的目标。”宋继强表示。

以下为演讲实录:

《新算力时代,实现万亿晶体管》

我们现在已经进入了一个数字化转型加速的时代,在未来我们需要持续长期的算力需求来去支撑这样的转型,英特尔通过长期的市场调研,还有一些我们在跟客户产品的开发交流过程中,我们发现有两个典型的趋势,这两个趋势都是跟数据的增长有关系:一个是量方面,数据在呈指数级增长,一个是在数据的形态方面日趋多样化。

左边这个图是展示了通过市场的分析报告梳理出来的数据量的增长,我们可以看到在2020年往后到十年间这个数据量增长是指数级上升,未来会达到10的30次方这样一个级别。主要驱动这些量增长的是现在很多虚拟世界里的数据绩效,从现在我们需要去做很多沉浸式的真实感的应用,到未来在虚拟世界里面还会有很多非真人驱动智能的,还有智能的机器人,到未来我们还会进一步把很多日常的经济活动、生产活动,通过数字化孪生方式的映射到虚拟世界里去,这同样需要大量数字化运算。

右边这张图展现的是未来的数据形态非常多样化,从现在大部分的数据还是可以通过人工去定义,通过程序化去处理,到未来非常多的数据是通过传感器,传感和感知进入到数字世界里,必须要通过像人工智能这样的方式去进行处理,并且实时反馈到物理世界中去,所以他们通常既具有实时性高的要求,又需要用人工智能算法处理。所以把这两个趋势结合起来,我们就可以发现,未来的数据量和质的变化一定需要新的算力去支持,而不是现在的方法就可以完全支撑的。

英特尔对未来算力的支持有很高的预期,并且我们有一个推测是到2030年,我们希望能够在单一个设备中去提供1万亿个晶体管,这个趋势如果去算一下,从现在一个设备中1千亿个晶体管,到2030年1万亿个晶体管,在未来7到8年是10倍的增长,所以这样一个增长的速率仍然是符合摩尔定律的增长曲线。我们可以看到,从左边这张图里面,过去40、50年增长的曲线一直是稳步在提升,而且通过英特尔很多内部的产品性能的分析可以看到,基本上是维持这样一个增长的速率。

在未来的几年,我们已经看到可以用几方面的技术来去继续推进这样的增长:首先包括RibbonFET这种环绕栅极的晶体管技术,还有PowerVia这种背部供电技术,这些都是在制成方面的。那么我们同时会继续去引进HIGH NA,也就是高数值孔径的EUA光刻机,同时会去叠加2.5D、3D封装的技术,来达到更高的系统集成度。

这张图展现的是从2000年后制成发展的一个路线图,其中大家会看到,英特尔在好几个关键的节点都产生出了非常重要的创新型技术来推动整个行业的发展。比如在应变硅、高K金属栅极、首个22纳米的FinFET3D晶体管,到未来我们会在英特尔的20A首先引入RibbonFET这种GUA的环绕栅极实现,未了我们会继续采用新的材料、新的工艺,去持续推进晶体管性能的提升,这些都是我们会在未来半导体的生产工艺制成方面进一步推进创新的很多技术。

随着半导体的制成工艺逐渐接近1纳米,甚至说推进到埃米级,就是1/10个纳米,我们会知道,继续靠晶体管萎缩来达到更高的集成度会越来越困难,成本也越来越高。为了进一步达到在单设备里增加晶体管密度的目的,我们还可以通过先进的封装技术去助力。先进的封装技术,从现在的2.5D已经可以在我们量产的产品里去使用的技术之外,我们还在推进3D的封装技术,就是Foveros的系列。Foveros的技术可以帮我们进一步去提高在垂直方向上整合主动芯片,也就是计算芯片和存储芯片的能力。同时我们还可以把2.5D的技术和3D的技术整合起来去使用,去建造更高层级的垂直水平复合整合的先进封装的芯片。提高封装技术的价值主要在于,我们通过高密度的互连,可以让多个制成工艺节点的芯片芯力集成在一起,可以让更大的裸片的复合体成为可能。

在最近的IEDM国际学术大会上面,英特尔发布了8个关于前沿组件技术方面的研究,这也是我们能够不懈推动摩尔定律不断前进的原动力之一。这张图展现了我们几个主要推进的创新部分,左边是新的3D封装技术,主要是通过Hybrid Bonding,也就是混合键合技术继续来实现芯力的无缝集成,我们可以实现种单芯片级别的这种芯片互连密度,把现在的互连之间的间距从10微米继续缩小到3微米级别,所以能够继续支持我们去进一步提高芯片集成的密度。中间这个展现的是我们使用新的超薄的2D材料,在未来的晶体管中去替代硅作为通道的材料,能够进一步去抗短沟道的效应,提高晶体管的效率和降低功耗。同时,我们还在量子计算量子比特的领域有进一步的探索,通过对于量子比特的缺陷分析来进一步提高我们去制造更大规模稳定的量子比特这样的效果。

右边是关于新的存储器件技术方面的研究,主要是基于铁电、反铁电技术,能够达到更高的存储密度,降低存储时延,从而使未来在嵌入式存储器里面达到更高的密度。同时,在新的三代半导体相关技术,我们在硅基的氮化镓芯片领域也达到了更高的性能比,可以为未来的5G、电动车领域提供更高的高功率功率器件。

我们进一步给大家解释一下先进封装技术可以给我们带来的优势。原来我们知道封装主要是把多个不同工艺的芯片可以组装在一起,可以是平面地把它们连接在一起,也可以在纵向去堆叠。原来的这种封装技术,通常是要在专门的封装工厂去使用封装系列的一些材料和工艺去制作,和晶圆生产相关的有些制成的材料和工艺要求差别是很大的。如果说我们想让封装层级的一些技术能够达到类似芯片,也就是晶圆级别的密度、功耗和它的制造工艺要求的话,要进一步去提升先进封装领域的很多技术要求。我们在英特尔去推动Hybrid Bonding这种混合键合封装技术的时候,就通过用新材料和新的工艺去能够在Wafer Fabrication,也就是晶圆生产厂里面去进行更多的3D封装的技术。这个就模糊了封装和芯片制造之间的界限,可以使用下一代的3D封装技术来实现一种准单片形式的芯片,这样可以把互连的间距继续萎缩到3微米,从而在面积层面上把功率的密度和性能提高了10倍。

同时我们还在新的这种工艺下面可以实现顶部和底部的芯力尺寸它的相对位置最大的灵活性,并且可以在两个方向上,就是纵向和水平方向上可以去通过在绝缘体里去通孔新技术能够解决未通孔电源和信号完整性问题。

刚才我们讲到的都是半导体器件层面制成方面的一些新技术,有了这些新的技术制造出来半导体材料,我们就有了更多的这种在架构上去创新的机会,我们在架构层面的话,会分成不同的处理器架构,根据它们去处理的数据类型可以分为CPU、GPU、IPU、IPGA或者说AI的专用加速器,我们统称为XPU。有这么多不同的加速器,不同的处理的芯片,我们其实可以对不同格式的数据进行分别有效的处理,同时会带来一个编程的困难,因为我们知道同时能够在多架构上编程的开发者是少之又少,如何去让未来的软件开发人员可以非常容易地使用到这些不同架构芯片的能力,并且让他们的程序在未来的新的XPU产生的情况下继续保持兼容性,这就是1API带来的效能。

同时,我们还发现需要一个开放的标准去把不同厂家的很多不同XPU甚至其他的IO器件、其他不同的芯力要能集成在一起,所以需要有UCle这种开放的芯片互连标准,把它们整合在一起,就形成了一个持续、超能、异构计算的完整布局,就是有架构级的创新,有软件级的生态,还有芯片互连的生态。

OneAPI是一个建立在开放统一的跨架构社区编程的模型,在这个社区里面的话,我们是在去推动一种基于标准的统一的软件堆栈,也就是说,最底层的各种CPU、GPU、XPU是可以来自各个不同的硬件厂商,它们需要做的就是大家在一个统一的硬件抽象层,就是community label zero,去描述和暴露他们硬件的能力。然后在中间就可以有很多各种不同的高性能库,可以去封装他们在做不同种类功能时候的一些能力。同时也可以用业界标准的clk的编程语言来去直接对这些硬件能力进行编程。所以有了中间这一层之后,上面的那些软件或者AI计算的框架就可以去无缝调用各种不同的SPU的能力,应用和服务就不需要去关心底下的硬件到底是使用的哪种搭配,或者说未来如何演进。

所以这样的一种方式就可以解放原来的私有编程模式,充分释放和挖掘硬件的全部性能。在未来还可以有一个统一的社区去做代码的维护,让开发者更加安心。

针对这样的一个OneAPI开放统一的框架,右边就展现了英特尔给出的一些基础的工具包,包括在Data Parallel时候的Native Code C++的编程,还有一些专门领域的工具包,都是可以提供给开发者去使用的。

刚才我们还提到了把不同的芯力连接起来需要统一的标准去互联互通,这个标准非常关键,因为它首先要能够保证各个厂商生产出来的硬件可以首先在物理层它们的电器层面进行无缝的对接,能够把各种各样的IO信号的完整性保证起来,然后才能在上面的信号数据传输协议层达到更好的统一的效果。所以在这样一个大的背景下,英特尔是积极推动建立了UCle这样的一个开放的联盟,首先是我们可以去支持把英特尔相关的处理器、英特尔相关的一些D2D I/O的技术,然后还有一些多芯片互连通信的技术、协议,都推送在这个标准里面,也会去支持对接很多其他不同种类的芯片,比如说Arm Risc,这些都是在开放的UCle联盟里面去对接的架构和芯片。

同时,我们还有3D封装的技术、2.5D封装技术,可以在这个互连的联盟里面去继续推进它的规范化和标准化。未来的话,我们希望在多个芯力的管理、安全性上面去达成更多的标准化的目标。

总之,在未来的芯片半导体这个领域需要非常多的各种各样的技术,在开放的领域去探讨和共进,我们相信在这个领域,创新是永不止步的,我们非常有信心在2030年实现在单个设备上达到1万亿的晶体管的目标。

谢谢。